Functional Verification Engineer

An often-overlooked part of chip design is Verification according to Sondrel, as designing the front end of a chip is generally perceived as being the more interesting part. However, Susan Mack, one of our Senior Engineering Managers, disagrees: “Verification is the critical part of the chip design process that can take up as much as 70% of the time. The Designers create a design to meet the specification and then Verification Engineers do their best to break it and that is where the exciting and interesting challenges are of thinking outside the box. Real life can create unusual scenarios for a chip and our job is work out ways to test each design to make sure it will perform correctly whatever situation is encountered as well as innovating to create new tools and methodologies.”

An often-overlooked part of chip design is Verification according to Sondrel, as designing the front end of a chip is generally perceived as being the more interesting part. However, Susan Mack, one of our Senior Engineering Managers, disagrees: “Verification is the critical part of the chip design process that can take up as much as 70% of the time. The Designers create a design to meet the specification and then Verification Engineers do their best to break it and that is where the exciting and interesting challenges are of thinking outside the box. Real life can create unusual scenarios for a chip and our job is work out ways to test each design to make sure it will perform correctly whatever situation is encountered as well as innovating to create new tools and methodologies.”

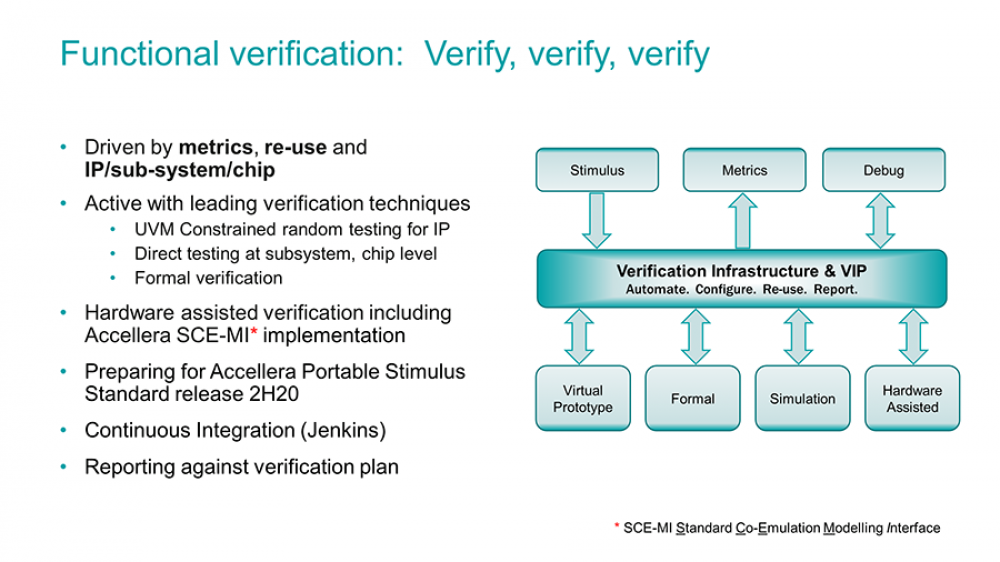

As chips become larger and more complex, it is vital to automate and re-use Verification tools and methodologies to speed up Verification and create testing scenarios. The latter are particularly important as such chips can have mission critical roles in self drive cars, for example, and must perform correctly whatever scenario occurs. A million to one event could be disastrous if the chip does not know what to do.

Sondrel has been investing in skills and SoC capabilities such as Architecture, Design and Functional Verification. As a result, it is now one of the leading Design Services companies in the world as it can provide a level of design unmatched outside of major semiconductor companies.

For example, it can blend C-based SOC integration verification with Horizontal and Vertical re-usability concepts and mechanisms. Vertical reusability means that Sondrel can re-use stimulus use cases, which are created on C-based verification flows and components, on the IP level, then sub-system and finally the SoC level so that use cases do not have to be created specifically for each level. This saves time and reduces the possibility of errors. With the Horizontal reusability approach, at a particular level, instead of running a simulation test that could take many days, Sondrel can run an emulation that takes only a few hours. Its test benches are designed in such a way that transition from Simulation environment to Emulation environment is easy and quick via an SCE-MI interface. A major time saving that quickly mounts up over many tests to really speed up time to market for customers.

Verification teams have integrated tools so that chips can detect and correct for errors

“Another example,” explains Kiran Kodakandia, the leader of one of Sondrel Verification Teams, “is that Sondrel’s UK, Indian and Moroccan offices have teamed up to create a new regression management tool. This is designed to create automated, constrained random testing checks to speed the verification process and generate detailed reports for engineers, management and the customer against milestones. This ensures high quality verification and less manual work so that engineers can focus on parts that need the application of their skills and creativity, providing a faster time to market for customers.”

Lastly, as part of its drive to innovate Verification, Sondrel has added a new design capability that would normally only be found inhouse at big semiconductor companies. Its verification teams have integrated tools so that chips can detect and correct for errors caused by radiation such as cosmic rays of solar flares. Known as latch-up, it is a type of short circuit which could have serious consequences in mission critical or safety critical applications such as in planes or cars. As chips become larger, the greater is the chance of a latch up occurring somewhere on a chip. The thinner feature sizes of smaller geometries also increase the possibility of latch up having an effect.